Moore’s law is dead sounds death of a king. By the way, why should we be concerned with this? The Economics of cramming more components onto an integrated circuit gave birth to an observation—Moore’s law. It tells that the number of transistors in a dense integrated circuit (IC) or microchips doubles every two years. It happened due to the success of lowering the cost and increasing performance by reducing the size of components and bringing them closer. Hence, an intense competition sustained over decades to keep Moore’s Law alive. But the same economics is on the way to meet the reality—Moore’s law is dead.

To keep Moore’s law alive, specialization started growing in every layer of the semiconductor value chain. Consequentially, the race of ideas, patents, and specialization led to the growth of monopoly across the industry. Furthermore, due to it, microchips started gaining increasing traction in fueling Reinvention waves, expanding the market of semiconductor devices. Consequentially, due to the success of making transistors better and cheaper, the semiconductor industry volume kept growing, reaching $600 billion in 2022.

But the economics of making components better and cheaper by doubling microchip density every 18 or 24 months has been slowing down. It’s becoming extremely expensive and complex to keep reducing the dimension—raising the question of whether Moore’s law is dead.

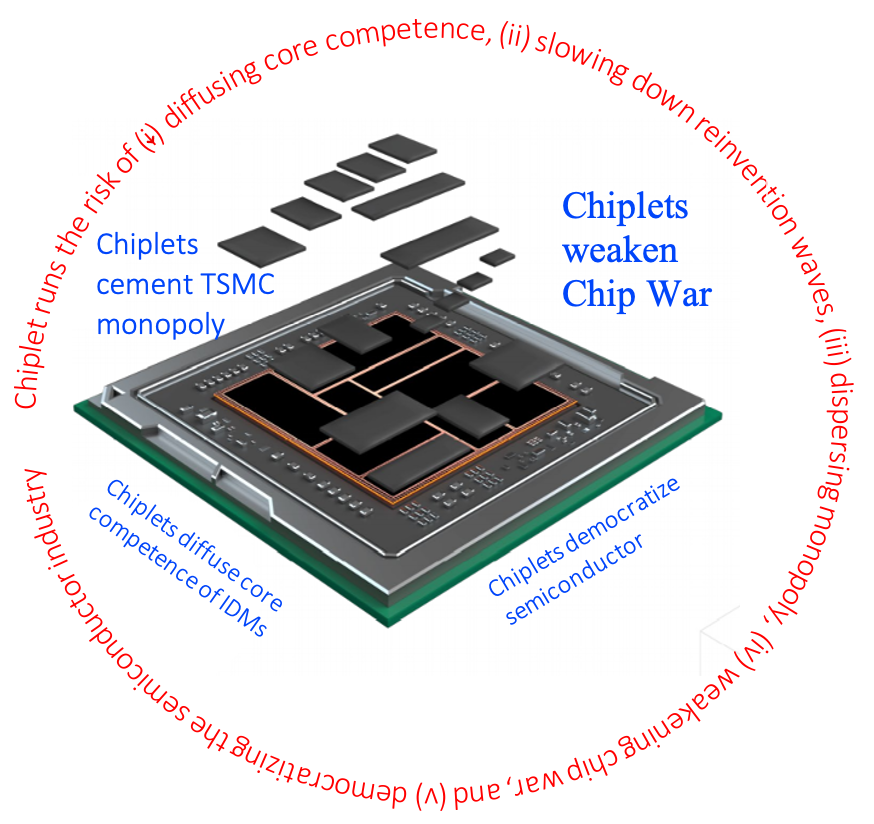

In the post Moore’s law era, the focus has been on dividing the system on a large monolithic chip (SoC) into smaller pieces or modules. They are produced as individual chips—chiplets. These chiplets are interconnected as 2.5D or 3D structures and packaged to offer a system in a package (SiP). Consequentially, the race of specialization shifts from chip density to package density. But such a change will likely redefine the semiconductor industry in the Chiplet era.

What is Moore’s law?

Moore’s law is not a natural law. It’s not like the energy-mass equivalence law (E = mc2), Ohm’s law (V = IR), or Hooke’s law (Fs = –kx). In 1965, while working at Fairchild Semiconductor, Dr. Moore shared an observation in a scientific paper that Transistor density in microchips doubled every 12 months. Later, he updated the period of doubling to 24 months; subsequently, he changed it to 18 months. Such observations led to Moore’s law which states that transistor density on a microchip doubles every 18 months.

As it’s not a natural law, what is the underlying force of doubling transistor density? The answer is plain and straightforward—the economics of making devices smaller and bringing them closer. It is based on the reality of making devices better and cheaper simultaneously by cramming more of them onto the same microchip or die area (square mm or mm2).

The production of the discrete transistor was costly. In 1957, Fairchild was selling transistors (part number 1211) for $150 apiece, costing $100 to produce. Due to using cheaper packaging and sourcing low-cost labor for bonding and packaging from Asia, the cost came down—leading to the $7 apiece RCA was charging in 1962. But the invention of IC in 1959 opened an era of producing multiple devices on the same die—opening the door to making devices smaller, better, and less costly.

Consequently, the race started to improve means like photolithography, etching, cleaning, bonding, packaging, and so on to increase microchip density. As a result, chip density kept rising, reaching 200 transistors per square mm in 1971, 275,000 per square mm in 2000, and 123.3 million per mm2 in 2020. Along the way, the cost of transistors kept falling from $100 apiece in 1957 to $500 per trillion transistors in 2021.

Semiconductor waves in Moore’s Law era—creating the demand

In 1947, there was only one transistor. On the 75th birthday, according to some estimates, the semiconductor industry produced almost 2 billion trillion devices in 2021. The obvious question: what is the underlying force of this staggering demand?

Due to the progression of microchip density in keeping Moore’s law alive, a growing number of products started experiencing reinvention. The reinvention waves kept growing due to the growing role of software running on increasingly more complex microchips. These reinvention waves kept making end-user products increasingly better, often cheaper. As a result, reinvented products kept diffusing deeper into society, creating exponential growth in demand for semiconductors.

In the 1950s, reinvention waves started in consumer electronics such as radio, television, and computers. Often, they began in a primitive form. For example, transistor radios and televisions were quite inferior to vacuum tube-based counterparts. But due to the advancement of making transistors better and cheaper, those reinvention waves kept progressing, resulting in creating a growing market for microchips. Another notable example has been the personal computer as the emergence of the minicomputer reinvention wave. In the beginning, PC was relatively primitive and far inferior to minicomputers. But the race to make processors and memory increasingly better and cheaper led to the expansion of the PC wave, creating a growing market for microchips.

Moore’s law is the underlying force of smartphone waves—creating demand for semiconductor

In the 1970s, telephone handsets had only a few semiconductor devices. Even Motorola Dynatec mobile handset had only a few thousand semiconductor devices. But a single chip A16 in iPhones alone has 16 billion transistors. As a result, the mobile handset industry contributed $116 billion in revenue to the semiconductor industry in 2020 (more than 20% of the industry). The phenomenal growth of transistor demand in the mobile handset industry has occurred due to the continuation of Moore’s Law. If microchips did not keep getting better at performing and less power-consuming, such a success could not have been a reality.

For example, according to Apple’s claims, the A16 (containing five times more transistors than A10) is about 40 % faster than the competition. It uses a third of the power of the best efficiency cores of other phones on the market. Hence, the continuation of Moore’s law has been the underlying force of continued Innovation in the smartphone, contributing to the growing demand for semiconductors. Hence, Moore’s law is dead is a serious concern for the future of the semiconductor industry.

Why Moore’s law is dead?

The race of specialization in keeping Moore’s law alive has been facing growing barriers. The first one is the physical limit–how more minor devices could be made is set by the dimension of atoms. The 2nd one is the growing capital expenditure and R&D cost for yield optimization. And the last most crucial factor is the modest largest defect size (20% of process node dimension)—negatively affecting the yield. Hence, there has been a sign of slowing down the rate of the growth of microchip density. For example, the Apple A16 chip processed using a 4nm process node of TSMC (Sept 2016) has less than 10% more transistors than that A15 produced a year ago (Sept 2011). On a macro scale, transistor count per mm2 has increased from 123.3 million in 2020 to 135.6 million in 2022—a 10% increase over two years.

Furthermore, there should be enough demand for reaching the minimum efficient scale of increasingly more expensive foundry nodes. For example, a 3nm foundry costs 20% more than its predecessor, 5nm. One of the primary reasons for cost escalation is the growing cost of lithography machines–increasing from $200 million for 5nm to almost $400 million for 2nm High-Na scanners.

So far, the invention of IC scaling down transistors in the 2D space of the silicon plane has been a smashing success. Consequentially, the transistor density in logic circuits has increased more than 600,000-fold since 1971. But as explained, packing more transistors in 2D space has been reaching the limit. But how is it feasible to stack transistors vertically? Like NAND flash memory, will it be economically attractive to pack transistors in vertical layers, building a skyscraper in the nanoworld? Success along this path may give another life to Moore’s law—improving performance and reducing the cost of microchips simultaneously.

Chiplet era begins

As Moore’s law is dead, we enter into a new era. In chip design and manufacturing, cost and performance are two pressing issues. In Moore’s law era, both of them were improving. But the shrinking chip dimension has been reaching the reality that cost increases along with shrinking dimension. Furthermore, performance improvement also has been slowing down. On the other hand, the projection window limit of the scanners constrains size growth. But there has been a growing demand to integrate more functionality or building blocks. Hence, the solution is to divide the system into modules and produce each separately as chiplets. Upon doing so, interconnect of required chiplets using 2.5D or 3D technologies ends up packaging them as system on package (SiP) instead of the system on chip (SoC).

As many chiplets could be produced with older process nodes, the cost could be lower due to lower fab investment and higher yield. Besides, once a chiplet is developed and reused, the cost of testing and verification could be reduced. But having SiP using chiplet runs the risk of trading off performance for cost advantage. In many applications, the size of the package and its performance highly matter. Due to using older process nodes and interconnect for packaging, the size of SiP will be larger than SoC for packaging identical numbers of transistors.

Furthermore, performance will suffer due to slow transistor dimension progress and data propagation latency through interconnects. Moreover, the energy footprint per million transistors will not shrink like in the past. Hence, despite cost reduction, chiplet-based SiP will likely slow down the diffusion rate of transistors. Besides, the chiplet era will likely reduce the intensity of race of specialization and monopolization, redefining the semiconductor industry.

Chiplet defines semiconductor future

For sure, a $150 apiece transistor could not have done much. Indeed, it could not have placed billions of transistors on our palms. It could not have created a $600 billion market for semiconductor devices—triggering the Chip War. The underlying force of this phenomenal growth, fueling reinvention, migration, and monopolization, has been Moore’s law. The continuity of it has led to making transistors (i) better performing, (ii) cheaper, (iii) smaller, and (iv) less emerging dissipating.

But as Moore’s law is dead, we have been entering the Chiplet era. Instead of making a single chip packaging, increasing the number of transistors, we have been dividing the chip into modules or chiplets and packaging them as a system in package (SiP). But such migration from Moore’s law to the chiplet era will likely transform the semiconductor industry over the next few decades. Here is a likely 7-dimensional snapshot of the unfolding future.

1. Chiplet risks growth

As explained, the semiconductor industry’s growth has so far come from the reinvention waves of one after another product. Not in the beginning, semiconductor was able to fuel these reinvention waves. For example, billions of discrete transistors could not have been soldered together to fuel the smartphone innovation wave, creating more than 20% demand for semiconductor devices.

Although Chiplet promises short-term cost reduction, this is not scalable. There has been no technology core underpinning chiplet to offer a scalable cost reduction path like photolithography shown in Moore’s law era. On the other hand, Chiplets’ cost reduction proposition has been trading off performance. Cost reduction alone did not make semiconductors powerful technology core to fuel reinvention, creating new demand for semiconductors.

It seems that Chiplet is a short-term cost minimization approach at the cost of performance. Some applications may find such a system attractive, creating short-term demand for SiP. But in the long run, SiP would not behave like SoC in powering new reinvention waves or exponentially expanding ongoing waves. Hence, it appears that the semiconductor industry’s growth and other industries’ growth due to semiconductor-powered reinvention will slow down.

2. IDMs’ core competence–Chiplet diffuses

In retrospect, Integrated Device Makers (IDMs) like Intel grew from humble beginnings to large corporations due to three core capabilities. They are (i) proprietary microchips to fuel new reinvention waves, (ii) the ability to keep designing those chips as larger and more complex ones, and (iii) proprietary process node edge to churn out those chips.

Due to these three capabilities, their business volume at a high margin kept growing due to the growth of the reinvention waves they were fueling. For example, Intel kept growing due to its success in fueling the personal computer wave creating the demand for its chips for both client end devise and servers. But Intel’s revenue and profit started to slow down due to the saturation of the PC wave. Consequentially, Intel lost both silicon edge and financial health. On the other hand, TSMC kept growing as it succeeded in enhancing process nodes to churn out increasingly complex processors for fueling smartphone waves.

IDMs like Intel have failed to fuel new reinvention waves despite some attempts. If they get stuck with performance for pursuing Chiplet, how will they find new reinvention opportunities to fuel? Hence, in the Chiplet era, IDMs risk suffering from the erosion of their core competence in fueling the growth and profit margin. Therefore, it raises questions about whether Chiplet is a recipe for survival, death, or uprising of IDMs.

3. Chiplet raises OSAT and Fabless

The chip let area focuses on dividing a large SoC into chiplets, producing them individually, and interconnecting them as SiP. Besides, SiP designers will also have the option of mixing and matching available chiplets. As a result, complexity and workload will likely be migrating from design and fabrication to packaging. As a result, the packaging layer of the value chain will gain higher traction. Hence, fabless IC companies will find OSAT firms increasingly more relevant to them. In an extreme case, they may successfully design SiPs using only off-the-shelf chiplets and directly going to OSAT firms to interconnect and package them as per the design.

Besides, IDMs have fallen behind in process nodes; they will be running short in proprietary ideas as complex SoC in their strongholds. Furthermore, there will be decreasing chip design complexity in the chiplet era. Such an unfolding reality will keep reducing barriers to fabless companies entering and expanding their footprints in the markets of IDMs. By pursuing a chiplet and fabless approach, AMD has already established a stronger position in the server market, which used to be Intel’s stronghold.

4. TSMC in the chiplet era–cementing monopoly

IDMs like Intel used to be TSMC’s archrivals in process node sophistication. In 1987, TSMC started the journey with a few generation-older process nodes. But due to profit making opportunity of advancing process nodes for churning out increasingly complex chips for fabless companies (like Apple or QUALCOMM) to power smartphone waves, TSMC focused on sharpening process yield optimization R&D. It also built a strong partnership with ASML in EUV photolithography. Consequentially, TSMC has emerged as the most sophisticated wafer processing foundry, keeping Intel a few generations behind. For example, while TSMC has been running 4nm volume production in 2022 to produce Apple’s A16 chip, Intel keeps struggling to migrate from 10nm to 7nm nodes.

Of course, there was an impending threat on TSMC due to Intel’s likely migration to the latest process nodes and offering fab services to fabless companies. But due to growing complexity and intel’s incapability to reach the required yield level in sub-10 nm nodes, Intel has opted for older processed nodes to produce chiplets. And its Chiplet strategy includes the role of TSMC to produce those chiplets which will be demanding the most advanced process nodes. Hence, TSMC’s monopoly in high-end silicon processing appears to remain uncontested during the chiplet era.

5. Lithography edge–chiplet weakens

Since the invention of the integrated circuit in 1959, the advancement of lithography started to project increasingly smaller dimension features. This race has been the underlying reason for decreasing device dimension and increasing chip density–keeping Moore’s Law alive. As successive process nodes keep offering lower cost per component and higher performance, foundries have been racing to upgrade their lithography machine. And to keep moving to the next light source with smaller wavelengths, lithography machine innovators like ASML, Canon, and Nikon have been breaking new ground. But the cost of R&D, lead time, and risk for delivering the next version of the lithography machine for moving to the next process node have been exponentially growing.

For example, to turn extreme ultraviolet (EUV) light source possibility into a sub-10-nm scanner, ASML had to invest more than $10 billion over 20+ years. As a result, the cost of lithography machines has increased exponentially from a few million in the 1990s to over $200 million for EUV lithography machines for 5nm process nodes. This cost will likely reach $400 million for a High-NA EUV machine for a 2nm process node.

The migration of focus from SoCs to SiPs will likely reduce the demand for the next-generation lithography machines, as many of the chiplets of SiPs will be fabricated using older process nodes. As a result, Economies of Scale advantage will come down. Consequently, lithography machine costs will increase due to a higher R&D expenditure per unit. Hence, lithography machine makers will increasingly find economic non-viability to fund R&D for moving to the next node—slowing down the lithography edge.

6. Chiplet weakens Chip War

The US strategy for winning the chip war has been to keep China a few process nodes behind. But as the Chiplet era will likely slow down the progression to the next process node, the scope and benefit of keeping a few nodes back will keep eroding. Besides, as chiplets will be off-the-shelf components produced by many fabless companies by taking the 3rd party foundry services, controlling the cross-border trade of chiplets will be challenging. Moreover, a growing number of chiplets will be developed using older process nodes. As a result, the USA will face an increasing challenge to sharpen and maintain a silicon edge over China in the chiplet era.

Due to the slowdown of the edge of process equipment, chemical and human expertise race to move to the next process node in the chiplet era, China will get increasing catch time. Moreover, the density of active patents will also fall. Hence, the focus on developing SoC using the next node to SiP runs the risk of weakening Chip war. Hence, winning chip war in the era when Moore’s law is dead will be a tough call.

7. Chiplet democratizes the semiconductor industry

The intense competition of moving to the next process node and designing more sophisticated larger SoCs has monopolized each layer of the semiconductor value chain. The underlying cause of monopolization has been due to outperforming competitors with (i) growing idea or patent base, (ii) expertise edge, (iii) exponentially growing R&D and capital expenditure, (iv) economies of scale, and (v) decreasing catch-up time. But the Chiplet era runs the risk of slowing down this race. Instead of the urgency of moving to the next node and designing exponentially growing larger SoC, the focus would be on designing and fabricating chiplets, choosing off-the-shelf ones, and interconnecting them as a system in package (SiP). Hence, new entrants will find a decreasing barrier. Consequentially, firms in aspiring countries will face fewer obstacles to making an entry. Therefore, Moore’s law is dead appears to be a blessing in disguise for them.

The likely entry route could be developing chiplets as off-the-shelf components. The next move could be designing SiP, followed by entering the packaging segment. Hence, by decreasing entry and scale barriers, Chiplet will likely contribute to the democratization of the global semiconductor industry.

Moore’s law is dead is not just a simple issue. The migration to SiP from SoC in the chiplet era will likely have multidimensional ramifications on the semiconductor industry. This article attempted to shed light on a few dimensions of the semiconductor industry, which will likely be affected by the chiplet era. Further investigation is needed to have greater clarity, predict unfolding reality, and have rational decisions accordingly.

...welcome to join us. We are on a mission to develop an enlightened community for making the world a better place. If you like the article, you may encourage us by sharing it through social media to enlighten others.

Related Articles:

- Chip War

- Semiconductor–illusive technology core changing world order

- Winning Chip War–fuelling reinvention waves for changing world order

- Chiplet Technology — a weak reinvention core?

- Semiconductor Economics–will Chiplet era slow down the growth?

- ASML–growing pearl gets caught in Chip War

- China’s Semiconductor Independence–prematurely caught?

- India’s Semiconductor Dream–pushed in the slow lane?

- Semiconductor Value Chain–globally distributed ecosystem

- Semiconductor IndustryWaves

- Intel Falling Due to PC and Mobile Waves

- ASML Lithography Monopoly from Sustaining Innovation

- Taiwan’s Semiconductor Monopoly – How did it arise?

- ASML TSMC Nexus Fuels Semiconductor Monopoly

- ASML Monopoly in Semiconductor — where is magic?

- SEMICONDUCTOR MONOPOLY DUE TO WINNING RACE OF IDEAS

- Semiconductor Industry Growth–personalities, new waves, and specialization underpin

- Transistor–technology core shaping global trade and power

- Loss of America’s Inventions–blame semiconductor economics?